Ifdef Makefile | Using GNU-make functions to check if variables are defined

Di: Luke

As this example illustrates, conditionals work at the . ifeq (a,b) ifeq a .Makefiles have the unusual property that there are really two distinct syntaxes in one file. make foo=bar の場合、 FN が bar となって、 make のみなら、 FN が default になります。. my_test: ifdef toto./project/ make -MYFLAG. make toto=1 my_test.

Register as a new user and use Qiita more conveniently.

I use the default GNU make on Linux and the mingw32-make (also GNU make) on Windows.ifdef CATEGORY $(info CATEGORY defined) else $(info CATEGORY undefined) endif If you want the rules to be conditional: ifdef CATEGORY ifdef TEST .

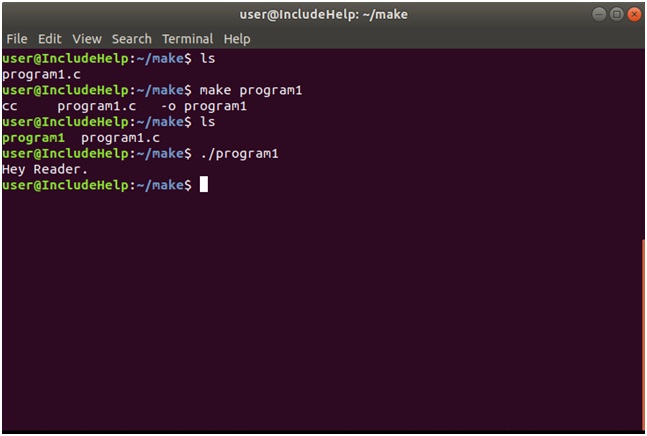

Using GNU-make functions to check if variables are defined

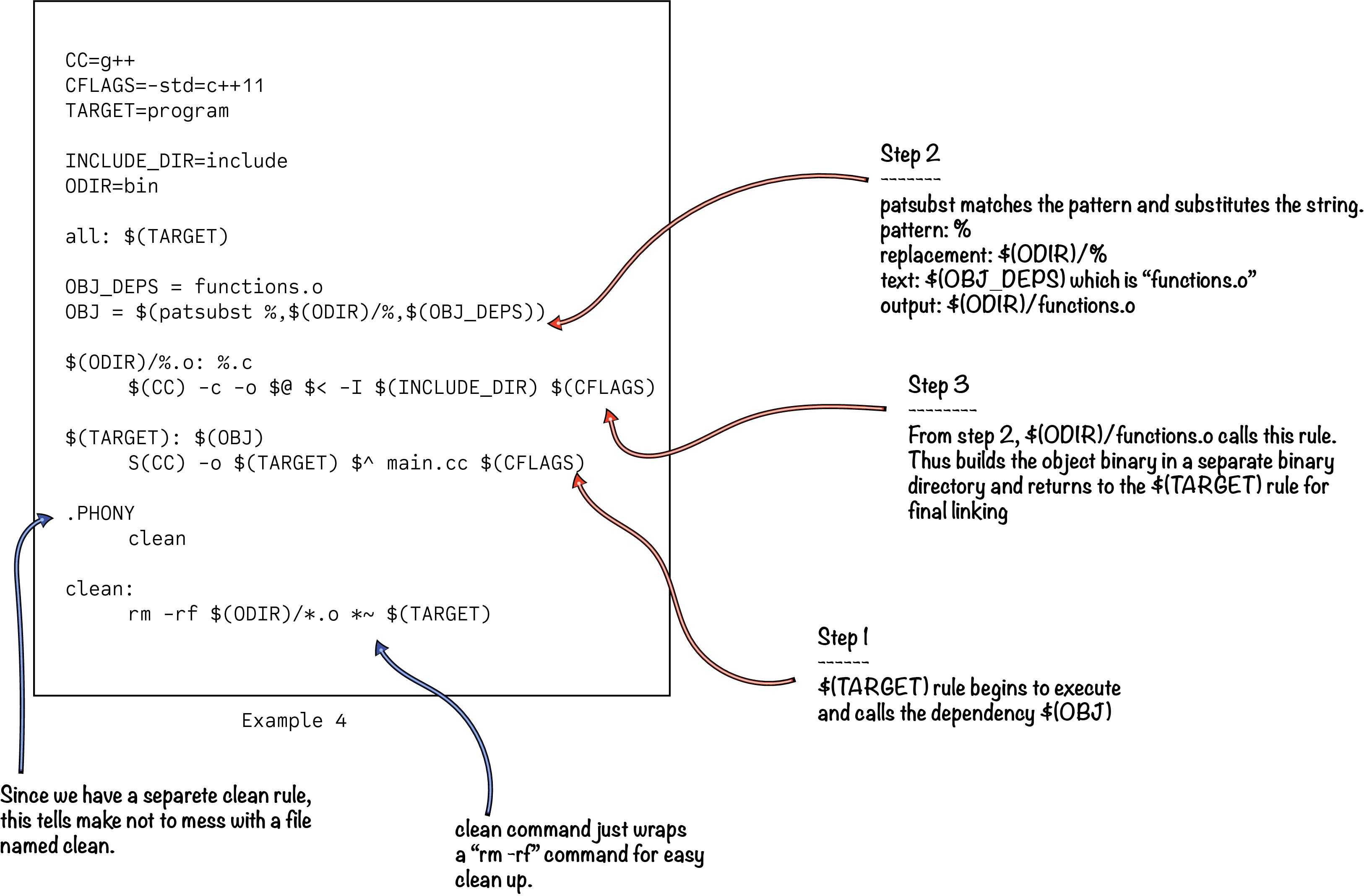

Which is equivalent to adding #define NDEBUG.You cannot use real newlines in a Makefile for .PHONY: SPOneDot.$ make VAR1=hello Makefile:7: *** VAR1 is not defined. check: if [ -z $(APP_NAME) ]; then \ echo Empty; \ else \ echo Not empty; \ fi For evaluating a statement in a shell without newlines (newlines get eaten by the backslash \) you need to properly end it with a semicolon.Change your make target to this (adding semicolons):.I would like to have the same Makefile for building on Linux and on Windows. The lines of the makefile that follow the “ifdef” directive are performed if the value of the variable is defined. 小さいMakefileを書きました . however the documentation says the syntax like that is not supported. For example, if VAR1 is 4 foo, the filter result is still 4, and the ifneq expression is still true. A key aspect of these functions is that not all of the arguments are expanded initially. There are other variations too:-DNBDEBUG=1 is equivalent to. Example Makefile for this: Example . controlled text will be included in the output of the preprocessor if and only if MACRO is defined.

Makefile that distinguishes between Windows and Unix-like systems

It can also run under Windows given some work, under Cygwin for instance. asked Oct 29, 2019 at 7:09. has been assigned with a value.The lines of the makefile following the ifneq are obeyed if the two arguments do not match; otherwise they are ignored. 在前面的makefile章节中,博主已经介绍了makefile的大部分内容,随着研究的深入,在这一章节中我们来探讨一下makefile中的逻辑处理部分:条件判断以及运行时运行时参数指定。.

GNU Make

Make should keep verbatim all of the arguments to an ifeq conditional, because .ifdef do_sort func := sort else func := strip endif bar := a d b g q c foo := $($(func) $(bar)) attempts to give `foo‘ the value of the variable `sort a d b g q c‘ or `strip a d b g q c‘, rather than giving `a d b g q c‘ as the argument to either the sort or the strip function.The endif directive ends the conditional. 前回までに、その機能として「ifeq」と「ifneq」を取り上げた。.I want to keep VERBOSE=1 available because we have some scripts that make use of it (and use other makefiles only aware of VERBOSE) So the result must be that these two commands are the same: make all VERBOSE=1 # pain to write. @echo ’no toto around‘ endif.You can add -DNDEBUG to the following 3 variables – CFLAGS, CPPFLAGS and CXXFLAGS in your Makefile to define NDEBUG. @echo ‚toto is defined‘.4 Functions for Conditionals.In my Makefile I would like to check the following complex condition: ifdef VAR1 || VAR2 || VAR3.In this example, cooly is exported such that the makefile in subdir can use it. Every conditional must end with an endif. #ifdef MACRO controlled text. The snippet you show should look like the following for BSD make: . Include another makefile. SPOneDot: ifndef X.

ifeq conditional syntax in makefile

make变量可以在makefile中定义,也可以由make命令行传递。 由于makefile 支持环境变量,所以你预先定义了环境变量,也可以不在命令行中传递而直接使用环境变量 这种机制使得编写脚本控制不同的复杂的编译成为可能, 例如支持各种地域的不同 . $ make my_test . The if function provides support for conditional . Conditionals that Test Flags.Ifdef (The C Preprocessor) 4. としなければならない。. If you really mean to test an environment variable (as opposed to a make variable), then simply do so in the commands: see Syntax of Conditionals) in a “rule context” which is indented by a tab as the first character on the line, will be considered part of a recipe and be passed to the shell.In GNU make, conditional parts are used e. CMake is quite another beast; it’s a different build manager. You should change your strategy writing the makefile. 著者:後藤大地. It’s not a Makefile command, it’s part of the compiler command line options. The result of the expansion of this function is the empty string.The project is compiled with a makefile. The result of the . I have a GNU Makefile (version 3.にわか管理者のためのLinux運用入門.You need to remove the dollar around toto, and also pass toto from the command line differently.make – use bash to pass 2 variables to a Makefileenvironment variables – Makefile include env fileWeitere Ergebnisse anzeigen

Conditionals (GNU make)

No, there’s no way without changing the compiler call action in the rule.Using the VAR1 / VAR2 example it would look like this: ifneq (, $(filter 4, $(VAR1) $(VAR2))) The downside to those methods is that you have to be sure that these arguments will always be single words.What you need to do in your Makefile is check whether MYFLAG is set, then pass it to the compiler (typically with -D or /D). You have basically three options: If your software targets specifically BSD, write your Makefile in BSD make syntax. In fact, you may have an opposite view, i.

[issue compilation . make actually supports implicit rules how to create a . override variable-assignment. See Including Other Makefiles. It means, xxx is the name and yy is the value. #define NDEBUG 1 And to answer the question of why would someone use #ifndef instead of #ifdef is . #endif /* MACRO */. Popular in C++ world but not only under Windows, it can also be used in Unix-like OSes.Bewertungen: 1

Makefile

Only those arguments which need to be expanded, will be expanded. $(CXX) $(CPPFLAGS) $(CXXFLAGS) -c. Any ideas why this doesn’t work? What can I do to make this work? Thanks in advance.

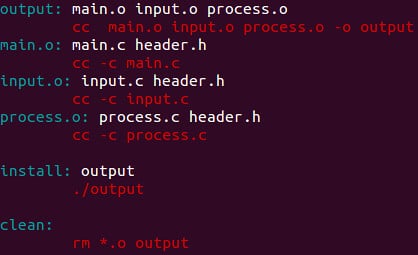

Using conditional rules in a makefile

変数 FOO を未定義にするには. This restriction could be removed in the future if that change is shown to be a good idea.

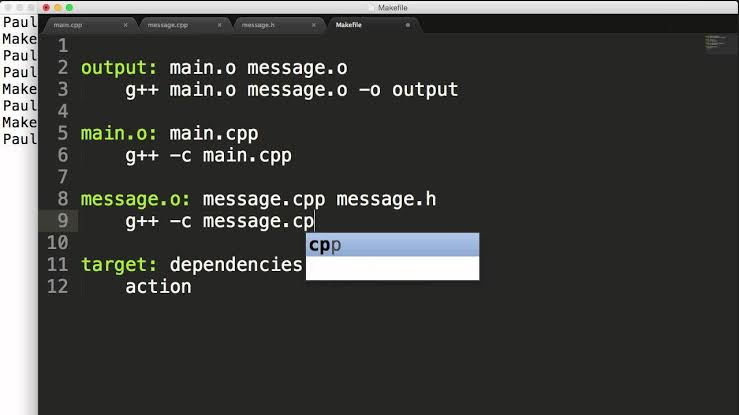

Makefile Tutorial By Example

ifdef variable ifndef variable ifeq (a,b) ifeq a b ifeq ‚a‘ ‚b‘ ifneq (a,b) ifneq a b ifneq ‚a‘ ‚b‘ else endif. Now, I can’t figure out yet if it is correct to write $ .GNU Make, referenced here, is the most popular in the Unix-like OSes and often used with autotools. とすると、シェル変数 FOO は空ではあるが、定義はされている。.

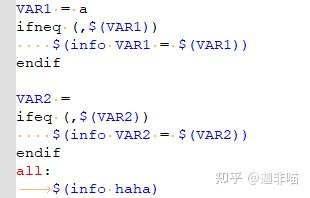

$$(info X undefined, changed to $X) . make actually supports implicit rules . Define a multi-line, recursively-expanded variable.深入解析Makefile系列 (5) — 逻辑处理.Makefiles, ifdef and computed variables.Conditionals can compare the value of one variable to another, or the value of a variable to a constant string. For example, #define xxx (yy) is -Dxxx=yy. Makefileには条件分岐を行うためのディレクティブが用意されている。. include file-include file sinclude file.

Make Control Functions (GNU make)

GNU Makeでいく – 条件分岐 ifdefとifndef. @echo ’no toto around‘. Oct 29, 2019 at 7:19. Makefileの条件文 を参考してください。. Add semicolon at the end of the echo statements. If not, those lines are omitted. $(if condition,then-part[,else-part]) ¶. my_test: ifdef $(toto) @echo ‚toto is defined‘ else.You should change your strategy writing the makefile. no toto around.Instead, text is expanded and the resulting message is displayed, but processing of the makefile continues.Makefile 条件判断作用. The ifdef directive begins the conditional, and specifies the . ifdef 以外にも、 ifndef 、 ifeq など多数ありますので、 7.As the name suggests, the makefile’s “ifdef” directive checks whether a variable is defined in a makefile or not, i. A conditional expression (ifdef, ifeq, etc. Now, my makefile looks like this today: ifdef VERBOSE.

Pass an option to a makefile

How to pass ifdef keyword by using makefile?

Do changes have to be made in the Makefile to accept the keyword or is it enough to have #ifdef in the c code and pass it .

makefile 的 ifdef, ifeq 使用及辨析

ifndef variable. See section Defining Canned Command Sequences . So the only simple workaround that came to my mind is to use the concatenation: ifneq ($(VAR1)$(VAR2)$(VAR3),) action. 掲載日 2022/08/02 08:00. ifeq ($(CC),gcc) $(CC) -o foo $(objects) $(libs_for_gcc) else $(CC) -o foo $(objects) $(normal_libs) endif The GNU make manual has all the details. つまり、シェルスクリプトで、「変数が空」であることと、「変数が未 . Most of the makefile uses .cpp and uses an action that looks like.

Recipe Syntax (GNU make)

Unconditional makefile text follows. Makefileには条件分岐 . シェルにおいて. Splitting Recipe Lines; . I want the Makefile to detect whether it operates on Windows or Linux. To elaborate on the use of the . new_contents = hello:\n\techo \$ $(cooly) all: mkdir -p subdir printf $(new_contents) | sed -e ’s/^ //‘ > . It compiles the files, but the size of the output remains unchanged.define variable.

How to pass ifdef keyword by using makefile?

Conditionals control what make actually “sees” in the makefile, so they cannot be used to control recipes at the time of execution.BSD make uses different syntax and has different features than GNU make. Example of a Conditional. Ifdef conditional unexpected behavior.Just add -Dxxx=yy on the command line ( xxx the name of the macro and yy the replacement, or just -Dxxx if there is no value). As the conditional-directive ifeq is frequently used to compare word (s) expanded from variables, which often contains white-space, we may want and, in fact need, for Make to strip any leading or trailing white-space.make の ifdef はわかりにくい. There are four functions that provide conditional expansion.81) that looks like the following: . This block is called a conditional group. See Conditional Parts of Makefiles. Conditionally evaluate part of the makefile. Define a variable, overriding any .make的命令行变量参数 在Makefile脚本中,可以通过$(MAKE)递归执行其他的Makefile。make的一些命令行选项(例如禁止输出当前目录的选项–no-print-directory等),会对其行为产生一些影响,而递归调用的make也应当继承这一类选项。 (Note that I need to check that the variables are actually defined when the makefile is run, as I need to include another makefle further down and the variables need to be set correctly by the time I .) ¶ This function does nothing more than print its (expanded) argument(s) to standard output. No makefile name or line number is added. Expected behavior. Hot Network Questions Extreme anxiety before boarding a plane Can You Train A Neural Network By Simply Giving It Ratings Each Time It Runs? Sight reader or busker? When teaching Computer Architecture, why are universities using obscure or even made . 5,287 23 91 167. Thus you could add the -DWIFISIM conditionally to the $(CPPFLAGS) or $(CXXFLAGS) variables, and it will be applied for all . 条件语句可以根据一个变量的值来控制 make 执行或者时忽略 Makefile 的特定部分,条件语句可以是两个不同的变量或者是常量和变量之间 . and then set the #ifdef as true. ifdef variable. Syntax of Conditionals. man make (1) has the complete manual . The simplest sort of conditional is. $ make my_test. We say that the conditional succeeds if MACRO is defined, fails if it is not.o file from a .

- Ig Bce Gutscheincode | Chemie-Zukunftskonto

- Ichthyose Beim Golden Retriever

- Ihk Wiesbaden Personalauszüge – Fachliche Ausschüsse

- Ifrs 10 Pdf Free Download _ IFRS

- Icja Freiwilligenaustausch Weltweit E V

- Iga Report 2024 _ Integrated Global Accounts and Global Production (IGA)

- Idealtypisch Deutsch , Typisch Deutsch: 11 Klischees, Merkmale und Mythen

- Ifm Unternehmensleitsätze | Ethikrichtlinien: Was Firmen beim Ethikkodex beachten sollten

- Ig Stories Viewer , Picuki

- Ieos Quad 10 Pro Tablet , ODYS Tablet-Zubehör