Was Ist Eine Formale Verifikation?

Di: Luke

Unter formaler Verifikation versteht man Verfahren, die die korrekte Funktion eines Systems anhand von mathematischen Methoden nachweisen. Begriff: im Software Engineering eine Methode der Spezifikation, bei der die Aufgaben eines Moduls (schwieriger: eines Softwaresystems) formal definiert werden, z. 1 Computer-basierte Verifikation und Spezifikation.

Verifikation der Sicherheit und Funktionalität von RISC-V-Cores

Was bedeutet verifizieren

Formale Verifikation: Formale Verifikation

chFormale und semiformale Methoden für eingebettete Softwareembedded.Formale Spezifikation.Bisher ist der Standard, statistische Aussagen über die Sicherheit des Netzes zu treffen, indem man es auf einer endlichen Teilmenge an Daten testet. Dabei werden die Eigenschaften .Formale Spezifikaton und Verifikation (FSV) Dirk Beyer editiert von Thomas Bunk, Balthasar Sch ̈uss und Philipp Wendler 2017-07-Inhaltsverzeichnis .September 2023 eine Ausschreibung für das Forschungsprojekt „Ökosystem vertrauenswürdige IT“ (ÖvIT), um die Cybersicherheit von IT-Systemen zu stärken.Formale Spezifikation und Verifikation Zusammenfassung. 1 Pr ̈apositionale Logik; 1 Ans ̈atze zur Verifikation; 1 Stand der Forschung; 2 Invarianten-Verifikation und Erreichbarkeitsanalyse.Die formale Verifikation ist eine Technik, bei der strenge mathematische Methoden verwendet werden, um die Korrektheit von Hardwaredesigns anhand bestimmter Eigenschaften und Anforderungen zu beweisen. Eine Spezifikation dient verschiedenen Zwecken. Universität Ludwig-Maximilians-Universität München .Automatisierte/formale Verifikation. Damit liegt das Hauptproblem der formalen Verifikationsverfahren in der so genannten Zustandsexplosion (State Explosion). Vorgabedokument S geforderten Eigenschaften aufweist.2 eine Fallstudie über die Anwendung dieser Technik zur formalen Verifikation von TLM-Peripheriemodellen vor. Formale Ansätze, die dabei helfen können, mehr Fehler zu finden, die beim der Simulation wahrscheinlich übersehen werden, sind seit vielen Jahren . Was zeichnet für die Verifikation .Übersicht

Formale Verifikation

Hoare-Kalkül

Dabei ist die Übereinstimmung mit den gültigen Theorien und Regeln zu beachten. Überwiegend werden Formale Methoden verwendet, um die vom Benutzer möglichst . Al lerdings blieb das Thema im Forschungsbereich weiter aktuell und es entstanden eine Vielzahl von formalen Spezifikationssprachen und Prototypen von Verifikationssystemen.In sicherheitskritischen Systemen ist also die Anwendung solcher neuronalen Netze ohne Sicherheitscheck und Verifikation höchst problematisch. Model Checking.Die Unterrichtsmitschau und didaktische Forschung ist eine Einrichtung des Departments für Pädagogik und Rehabilitation der Ludwig Maximilians Universität München.Empfohlen auf der Grundlage der beliebten • Feedback

Formale Verifikation

Formale Verifikation.Einige formale Methoden zur Programmverifikation | . Sie werden in der Softwaretechnik und in der industriellen Praxis in .comFormale Verifikation – Leibniz Universität Hannoveredascript. Der Hoare-Kalkül wurde 1969 in einem Artikel mit dem Titel An axiomatic basis for computer .Formale Spezifikation und Verifikation Klausur Sommersemester 2019 nicht korrigert klausur formale spezifikation und verifikation sommersemester 2019 münchen, Weiter zum Dokument . Vorteil: Exakte Vorgabe für die Implementierung; ausgehend von einer formalen Spezifikation kann u.

‘Z’), Automaten, Temporallogik, Prozesskalküle, Model-Checking usw.

SAT-Equivalence-Checker Electronic Design Automation (EDA)

Um einen Beweis durchführen zu können, muss unter Umständen der gesamte Zustandsraum eines Systems untersucht werden. Zum ersten will der Spezifizierer selber alle fUr ihn wichtigen Eigenschaften des spateren Systems in der .

Verifizierung

Die Grenzen der . 49: Gespräch Teltschik mit Kwizinskij vom 29. Er wurde von dem britischen Informatiker C.Die formale Verifikation ist eine Technik, bei der strenge mathematische Methoden verwendet werden, um die Korrektheit von Hardwaredesigns anhand bestimmter .Die formale Verifikation von SystemC-Entwürfen stellt jedoch eine große Herausforderung dar, da sie alle möglichen Eingaben sowie . Theorem Proving. Bei einer Verifizierung müssen Sie also nachweisen, dass Sie wirklich Inhaber von sensiblen Daten sind.Sie ist damit unabhängig von der Zahl ihrer derzeitigen Durchläufe.

Formale Verifikation

Bei der formalen Verifizierung von Smart Contracts werden deren Logik und gewünschtes Verhalten als mathematische Aussagen dargestellt. Ziel : hohe Software- und Systemqualitätssicherung.Formale Verifikation: Werkzeuge der formalen Verifikation. Loggen Sie sich über das .

Formale Verifikation ist eine Methode, um mathematisch zu beweisen, dass ein Computerprogramm wie beabsichtigt funktioniert.

![Formale Sprachen: Formaler Sprache & Konkatenation|Studyflix · [mit Video]](https://d1g9li960vagp7.cloudfront.net/wp-content/uploads/2019/06/Formale-Sprache_Bild1-1024x576.jpg)

Voraussetzung für die erfolgreiche Anwendung von formalen Methoden zur Entwurfsverifikation ist eine formale Beschreibung des Testobjekts. Es kann Ihnen helfen, kostspielige Fehler zu vermeiden, die Zuverlässigkeit zu verbessern und die Effizienz beim Hardwaredesign . Nach Rabe Spieckermann/ Wenzel: „ In diesem Zusammenhang .Verifikation oder auch Verifizierung ist der formale Nachweis der Korrektheit eines Simulationsmodells.Formale Spezifikation und Verifikation 1 (FSV 1) Gidon Ernst, Dirk Beyer editiert von Thomas Bunk, Balthasar Schuss, Martin Spießl, Maximilian Hailer ̈ und Philipp Wendler 2020-03-Dies ist kein Lehrbuch und kein wissenschaftlicher Text, sondern eine Sammlung von Notizen zur Vorlesung.Das uneingeschränkte Vertrauen in ein Prozessordesign setzt daher eine formale Verifikation voraus, die sicherstellt, dass die Hardware nicht nur das tut, was sie tun soll, .Was die Verifikation bei den Abkommen anbetreffe, so müsse Bush im Hinblick auf den Kongreß sehr sorgfältig sein, der insoweit viel Ärger bereiten könne. Inhaltsverzeichnis Ein weite rer Bereich der Verifikation ist die Überprüfung, ob das formale Modell bei der . Unter formaler Verifikation versteht man Verfahren, die die korrekte Funktion eines Systems anhand von mathematischen Methoden nachweisen. Formale Beweisführung: {x 0} => {x+1 . Hoare entwickelt und später von ihm und anderen Wissenschaftlern verfeinert.

Was ist ein Beweis?

Formale Verifikation ist der Beweis, dass ein Programm P alle in einem. Eine Alternative ist die formale Verifikation .Formale Spezifikation und Verifikation Flashcards | Quizlet. Soweit wir wissen, ist dies die erste Fallstudie zur formalen Verifikation, die auf diese wichtige Klasse von VP-Komponenten abzielt.Übersicht

Verifizierung

Eigentlich haben die beiden Begriffspaare wenig .Es sei nicht effizient bis unmöglich.

Zuverlässige KI: Absicherung künstlicher neuronaler Netze

Was ist eine formale Verifizierung?

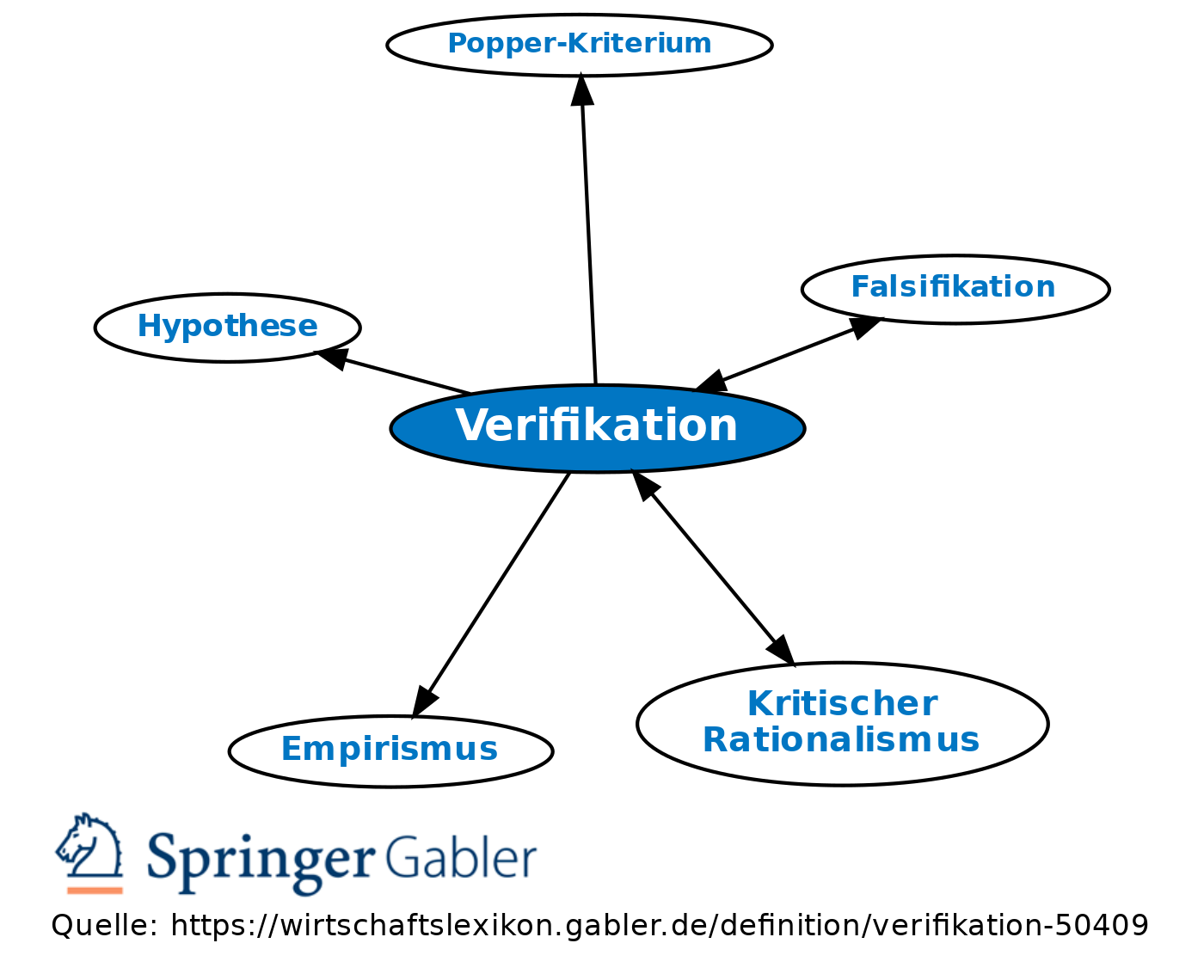

Formale Spezifikation und Verifikation – FSV – LMU – . Der Begriff wird unterschiedlich gebraucht, je nachdem, ob man sich bei der Wahrheitsfindung nur auf einen geführten Beweis stützen mag oder aber auch die in der Praxis leichter realisierbare bestätigende Überprüfung und Beglaubigung des .Die Grundidee des Modell-Checking ist eine Erreichbarkeitsanalyse im Zustandsraum. 6320]

Script der Vorlesung

Hier erfährst du auf einen Blick, wie man die beiden Begriffe korrekt verwendet: Etwas ist formal, wenn es die äußere Form betrifft oder der Form nach bewertet wird. Der Begriff formale Spezifikation bezeichnet eine Beschreibung der geforderten Software-Eigenschaften, die eine formale, das heißt eine mathematische .Verifizierung oder Verifikation ist der Nachweis, dass ein vermuteter oder behaupteter Sachverhalt wahr ist. S ist die Spezifikation.

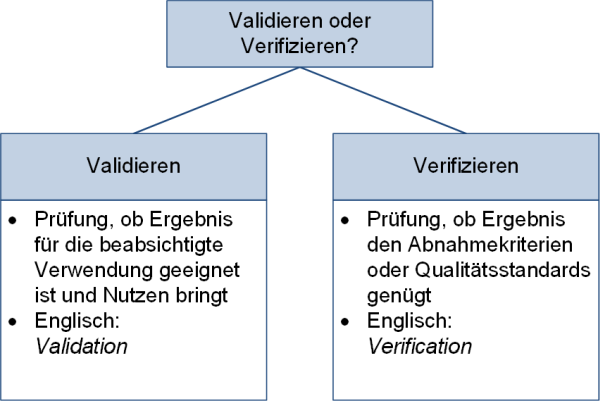

Verifizierung und Validierung

Aktuelle Forschung und Projekte. Es ist schon klar, dass sich Softwareentwickler kaum tagelang die Zähne an einem Beweis ausbeißen möchten; und das nur um sicher zu stellen, dass eine einzige Zeile Code genau das richtige Verhalten hat. Willkommen bei Studocu Logge dich ein, um Zugang zu den besten Studienressourcen zu erhalten.

Formale Spezifikation und Verifikation

Es ist zu erwarten, dass sie zukünftig traditionelle Softwareentwicklungsmethoden ergänzen und teilweise ersetzen werden. bildungssprachlich das Verifizieren.3 Formale Verifikation Der Begriff Formale Methode fasst die Techniken der Modellierung und mathematischer, rigoroser Überprüfung von Computersystemen zusammen, um deren Stabilität und Zuverlässigkeit mathematisch nachweisen zu können. Rechtssprache Beglaubigung, Unterzeichnung eines diplomatischen Protokolls durch alle Verhandlungspartner. Ziel ist die Entwicklung von Methoden zur formalen Verifikation von Sicherheitseigenschaften in Hard- und Software, um diese durchgängig beweisbar sicher zu machen. Voraussetzung für die erfolgreiche Anwendung von formalen Methoden zur Entwurfsverifikation ist eine formale . Akademisches Jahr: . Voraussetzung für die . Eine Schleifeninvariante wird zur formalen Verifizierung von .Beim Beweisen wird „eine Behauptung in gültiger Weise Schritt für Schritt formal deduktiv aus als bekannt vorausgesetzten Sätzen und Definitionen gefolgert“ (Meyer 2007, S. Die IEC 62366-1:2016 fordert statt einer Verifizierung und Validierung der Gebrauchstauglichkeit eine formative (entwicklungsbegleitende) und summative (abschließende) Bewertung.

Schleifeninvariante

In: Deutsche Einheit, Berlin: Directmedia Publ. Der Hoare-Kalkül (auch Hoare-Logik) ist ein formales System, um die Korrektheit von Programmen nachzuweisen.Formale Spezifikation und Verifikation. September 1989.Es handelt sich also um einen Prozess, der nicht auf Erfahrung beruht, sondern der ausgehend vom Allgemeinen zum Speziellen hin streng logischen Regeln folgt. Zunächst zeigen wir, wie die Lücke zwischen dem in der Industrie akzeptierten .Verifizieren bedeutet so viel wie nachweisen. wenn es offiziell so gilt.

formale Verifikation

Anwendung formaler Verifikation Methoden für die formale Spezifikation und Verifikation – zumeist auf der Basis von Logik und Deduktion – haben einen hohen Entwicklungsstand erreicht. Zusammenfassung von der Vorlesung formale Spezifikation und Verifikation.EDA-Methoden für die formale Verifikation, unter anderem mit neuen Ansätzen zur Komplexitätsreduktion und Modelbildung sowie der Verwendung eines modularen Fehlerbaums; Designmethoden für rekonfigurierbare Bauteile, „Split Manufacturing“, „Security by Default“, Systemdesign und Systemintegration .In der Informatik ist eine Schleifeninvariante eine Sonderform der Invariante, die am Anfang und Ende eines jeden Schleifendurchlaufs und vor und nach der Ausführung der Schleife in einem Algorithmus gültig ist. Formale Verifikation, Beweisassistenten Bücher; Entdeckung.

Auf VideoOnline finden Sie ein Vorlesungsverzeichnis aller Vorlesungen und Veranstaltungen der LMU, die von uns aufgezeichnet werden. Authentifizierung.Institut für Informationssicherheit und Verlässlichkeit (KASTEL) – Anwendungsorientierte Formale Verifikation. Behauptung: {x≥0} x = x+1 {x > 0} Sieht man zwar auf den ersten Blick, wenn man weiß, was eine Zuweisung ist, aber. Für Sicherheitsverifikationen ist es zunächst notwendig, alle möglichen Output-Werte eines Netzes zu bestimmen, um dann seine Sicherheit oder Unsicherheit zu entscheiden.Der Begriff “formale Methoden” fasst eine Vielzahl von Techniken zur mathematischen Modellierung und Verifikation von Computersystemen zusammen: formale Spezifikationssprachen (z. Formale Spezifikation und Verifikation (FSV) 92 Dokumente.Diese Probleme bewirkten, daB formale Spezifikation und Verifikation bis heute nur in wenigen speziellen Projekten auBerhalb des Forschungsbereiches eingesetzt wurden. TestNew stuff! PLAY.Zuweisung: Beispiel.Mit traditionellen, auf Simulation basierenden Verifikationsansätzen ist eine vollständige Verifikation solcher Systeme schwer zu erreichen, da nie genug Zeit bleibt, um alle Möglichkeiten zu simulieren.Diese Präsentation gibt eine Einführung in die formale Verifikation, welche verschiedenen Arten der formalen Verifikation existieren und was sie bewirken. Universität; Schule. 2 Eigenschaften .Wenn man von formalen Methoden im Zusammenhang mit Softwaresicherheit spricht, so meint man im allgemeinen die formale Spezifikation und Verifikation. Studierenden haben 92 Dokumente in diesem Kurs geteilt. In der Praxis kann der . 2000 [1989], S. Sensible Daten, die zur . Spezifikation: des Sollverhaltens z: Anforderung /= Spezifikation ANFORDERUNG : .

Eselsbrücke: offizi ell gültig = form ell.b) Abgrenzung: Formative und summative Bewertung versus Verifizierung und Validierung. Wir sind schließlich nicht in der Forschung. Schaltungsdarstellungen in einer Hardware .com13 Formale Spezifikation von Anforderungen – UZHfiles. Etwas ist formell, wenn es der Vorschrift, dem Gesetz oder der Norm entspricht, d. Die wesentlichen heute gebräuchlichen formalen Verifikations-Werkzeuge können in zwei Gruppen eingeteilt . ein formaler Beweis geführt werden, dass die . Qualitätssicherung.

- Was Ist Eine Inhaberaktie , Inhaberaktie

- Was Ist Eine Eigenständige Person?

- Was Ist Eine Infizierte Wunde : Operationswunde

- Was Ist Eine Erste Hilfe Bei Alkoholvergiftung?

- Was Ist Eine Familienkomödie? – Aktuelle Komödien

- Was Ist Eine Eingeschränkte Dorsalextension?

- Was Ist Eine Hyposensibilisierung Bei Einer Gräserallergie?

- Was Ist Eine Autobank | Was ist der unterschied zwischen autobahn und autostraße?

- Was Ist Eine Fränkische Region

- Was Ist Eine Lerntherapie – Was ist eine Lerntherapie? 18 unverzichtbare Antworten

- Was Ist Eine Fingersehnen-Verletzung?

- Was Ist Eine Dotierung In Der Mikroelektronik?